**Laboratory

of High Energy Physics

Data Analysis**

Tomsk

State

University

10.11.2025

## Отчет группы электроники за октябрь

Бернгардт Андрей, Ерофеев Дмитрий, Жидков

Кирилл

# Коротко

- 1) Проверяли интерфейс QSFP на работоспособность.

- 2) Тестируем DDR4, чтобы в дальнейшем использовать в кластеризации данных.

- 3) Продолжаем разработку прошивки для on-tablet-counter.

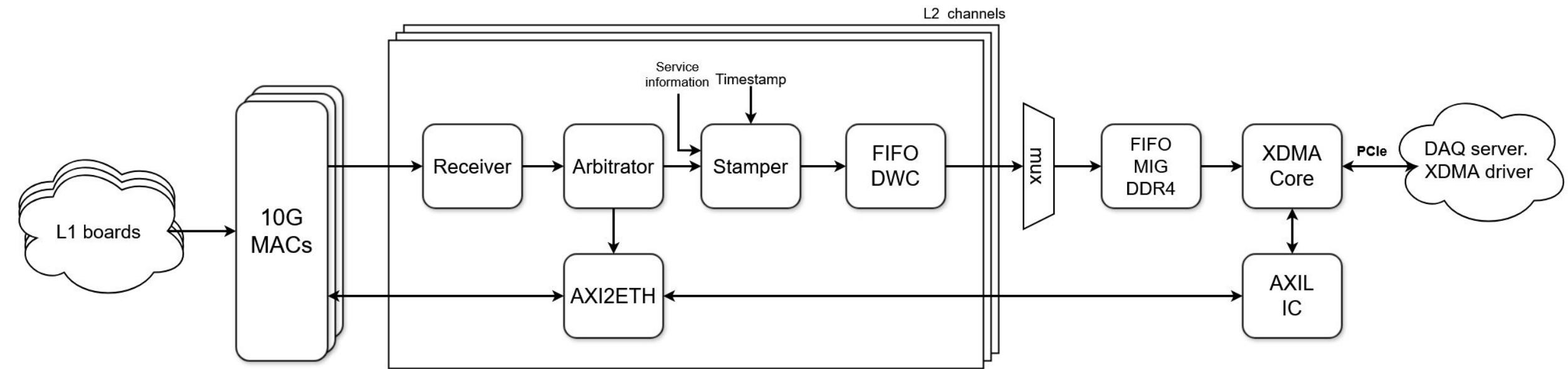

# L2 concentrator

- 1) Прием данных от нескольких (8 - 16) концентраторов первого уровня (L1).

- 2) Кластеризация данных в виде удобном для read-out компьютера.

- 3) Передача “медленных команд” на L1.

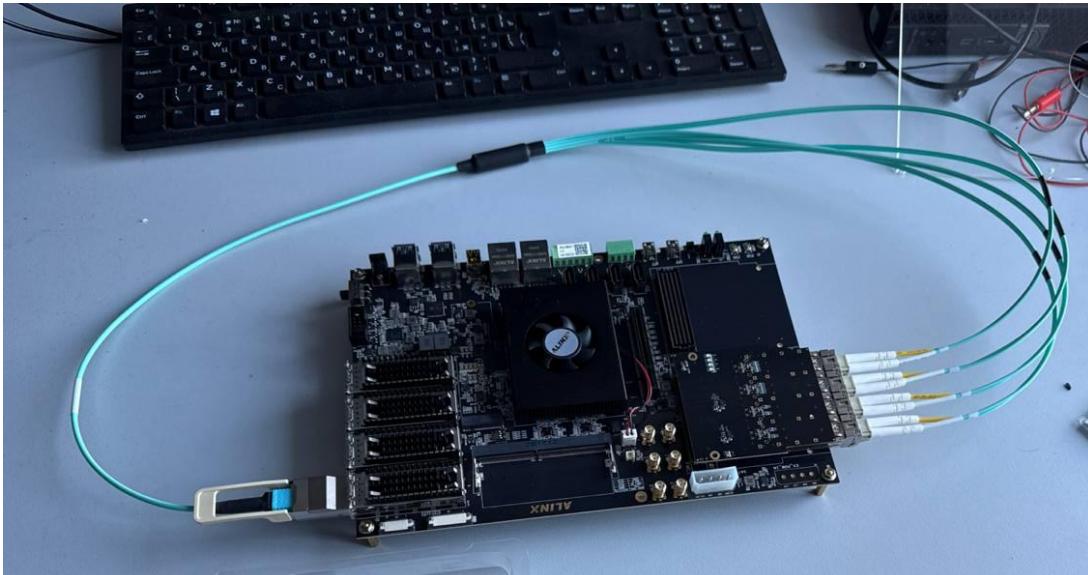

# L2 - тесты QSFP

ALINX Z19 with QSFP and SFP transceivers

- Собрали прошивку для платы Z19 с поддержкой QSFP и SFP. Провели тесты пропускной способности. Никаких отклонений не обнаружено.

- QSFP позволяет подключать 16 плат L1 к одному L2 концентратору.

- Коллеги из Дубны планируют разработать прототип L2 с QSFP (к лету)

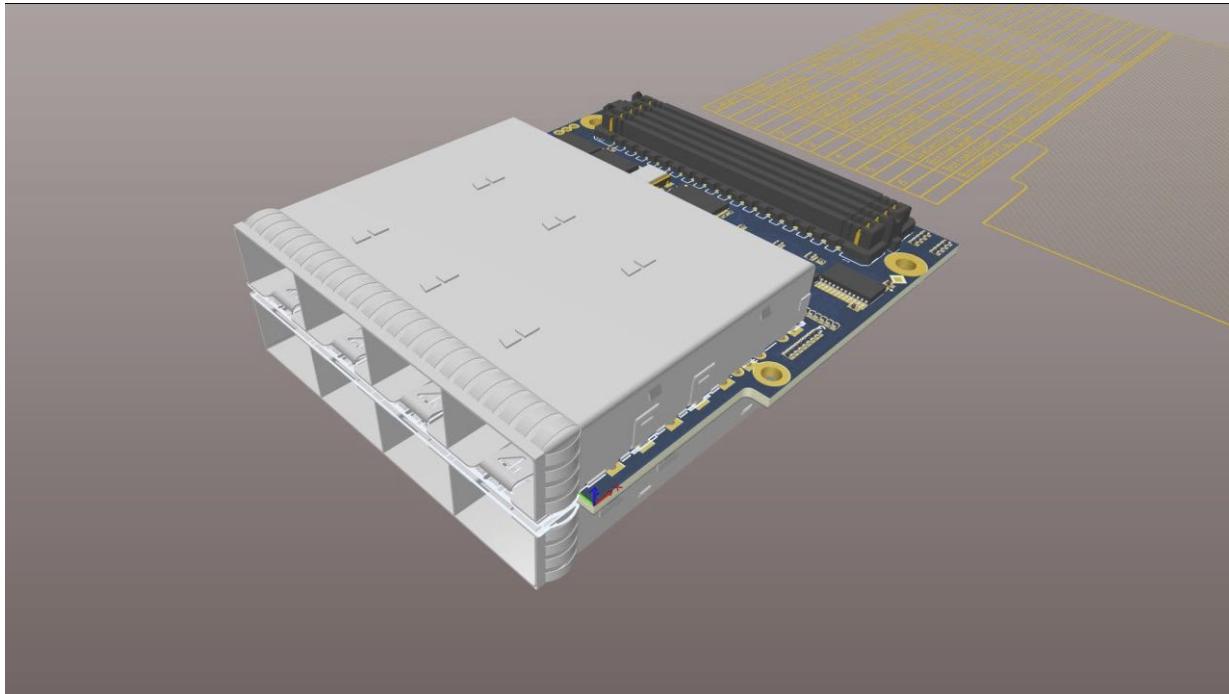

# 8x 10G SFP+ FMC

FMC на 8 SFP корзин

- Все для сборки компоненты платы были доставлены.

- Сама сборка пока затягивается

# L2 - Кластеризация

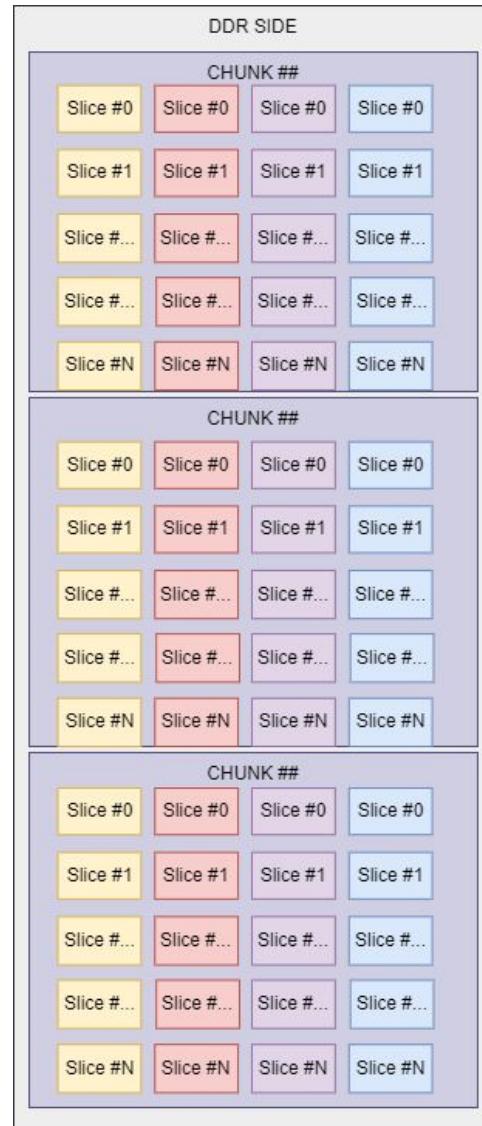

Архитектура модуля для кластеризации данных

- Алгоритм кластеризации данных на плате

- Планируется разработать два формата организации данных в буфере и выбрать эффективный.

- Буферизация в памяти DDR4

Возможная структура буфера

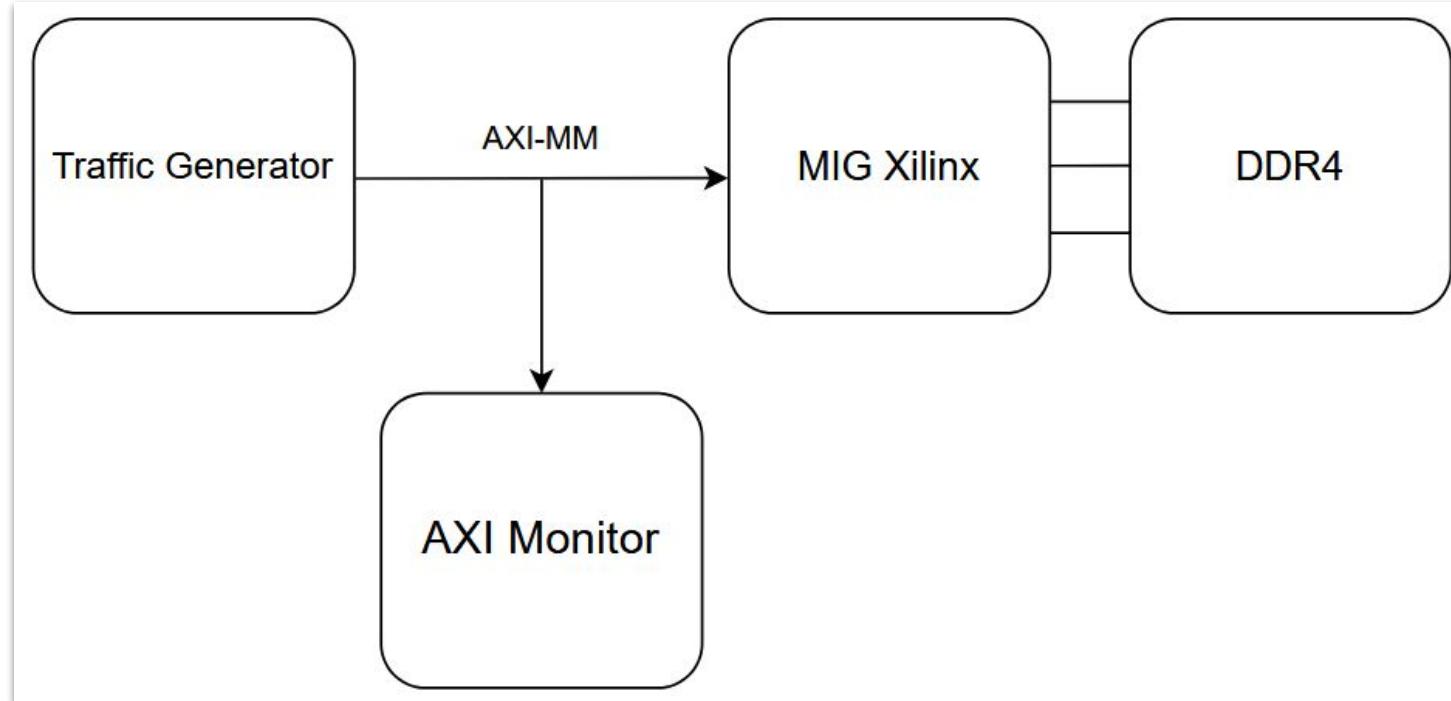

## L2 - тесты DDR4

- Тестирували DDR4 при помощи встроенных инструментов для тестирования .

- За 3 и 6 часов теста ошибок не обнаружено.

- Добавляем AXI-Monitor, чтобы следить за транзакциями и пропускной способностью в teste

- После тестов добавим DDR4 и MIG в архитектуру L2

Схема теста памяти DDR4 (с Monitor-ом)

MIG - Memory Interface Generator

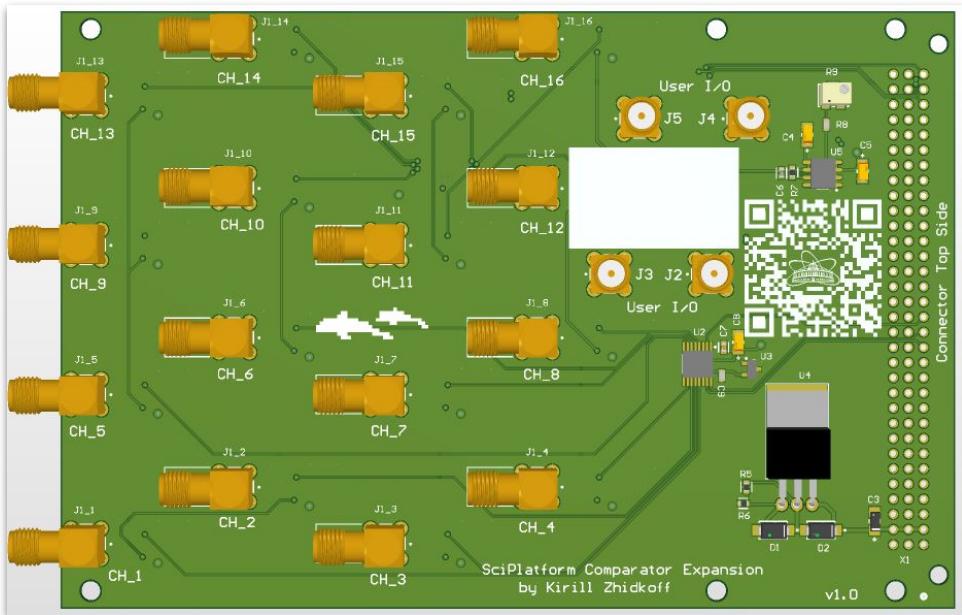

# On-table counter

Плата расширения на 16 каналов

Несущая плата с ПЛИС

Гибкая платформа для тестирования детекторной электроники.

Разрабатывается на плате с ПЛИС. Также разработали плату

расширения на 16 каналов.

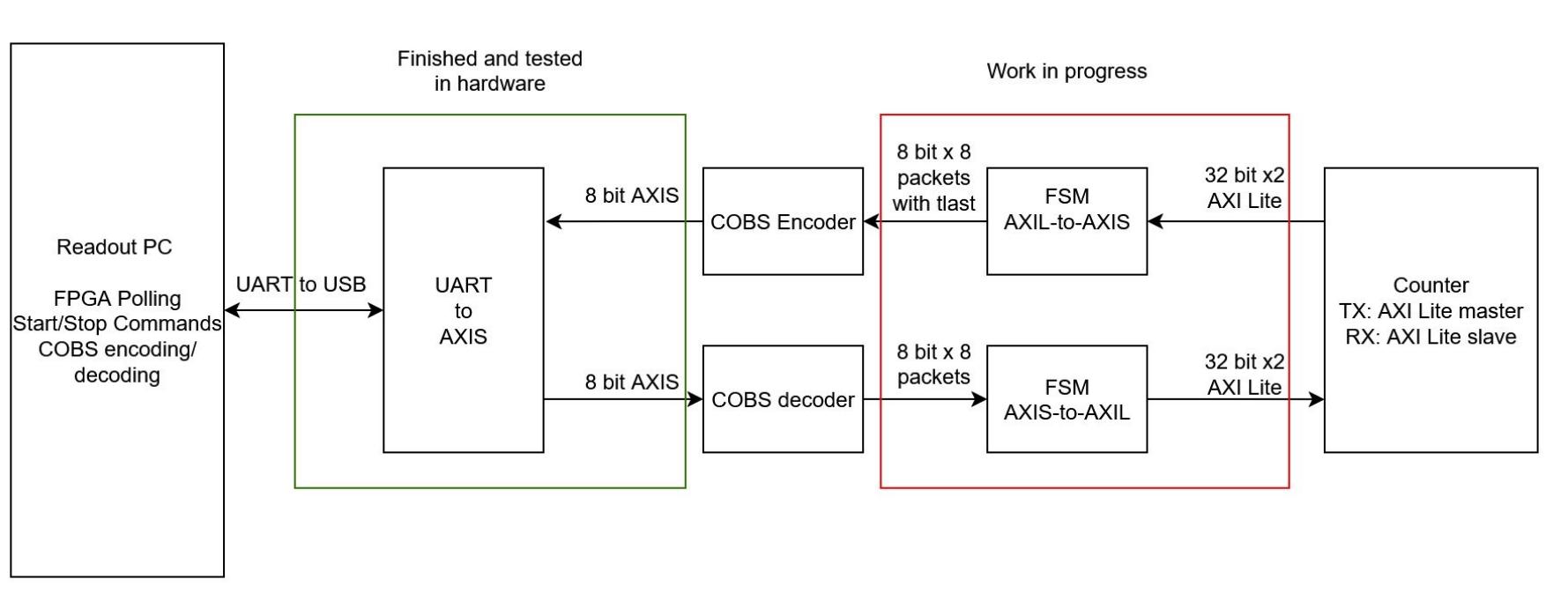

# on-table counter - статус

Архитектура прошивки

- 1) Протестировали интерфейс UART-AXIS

- 2) Написана программа для чтения и записи через UART с ПК.

- 3) Работаем над конверторами для интерфейсов

Чтение-запись внутренних регистров, отвечающих отдельному детектору.

Разделение пакетов при помощи Consistent Overhead Byte Stuffing (COBS).

# Планы

- 1) Переделать логику работы с “медленными командами”.

- 2) Закончить тестирование DDR4.

- 3) Внедрить MIG, DDR4 в архитектуру платы и приступить к разработке алгоритмов кластеризации .

- 4) Дописать логику прием-передачи данных пакетов в on-table counter.

- 5) Планируем с коллегами из Дубны в следующем году публикацию 3-х статей.

# Thank you!

## Laboratory of High Energy Physics Data Analysis

Tomsk

State

University

**National Research

Tomsk State

University**

36, Lenina Avenue, Tomsk, 634050, Russia

Tel.: +7 (3822) 529 852, fax: +7 (3822) 529 585

E-mail: [rector@tsu.ru](mailto:rector@tsu.ru)

[www.tsu.ru](http://www.tsu.ru)