### NICA SPD L2 concentrator firmware

Vladislav Borshch Laboratory of HEP TSU

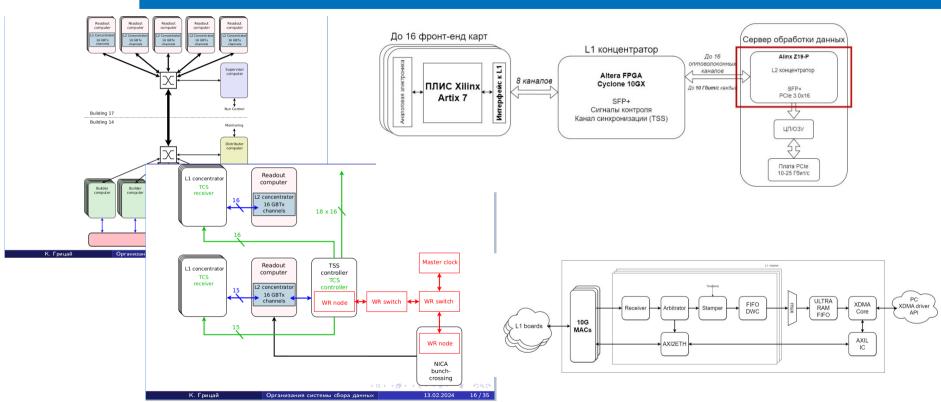

# NICA DAQ system

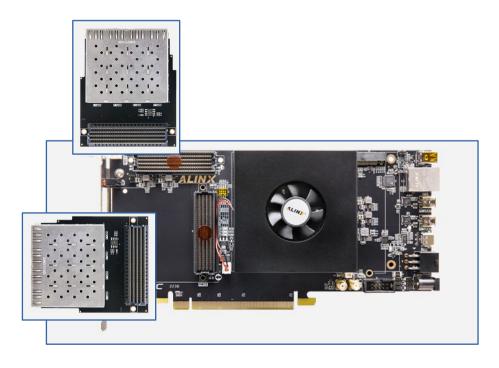

## L2 concentrator platform

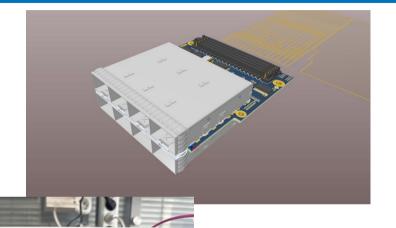

- Full setup based on Alinx Z19-P board

- Up to 8(16) 10G SFP channels (L1 links/boards)

- PCle Gen 3.0 x16

- MPSoC XCZU19EG chip

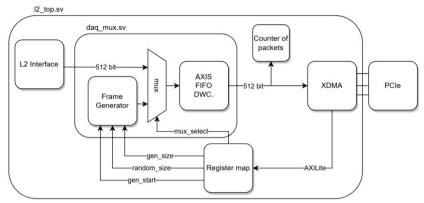

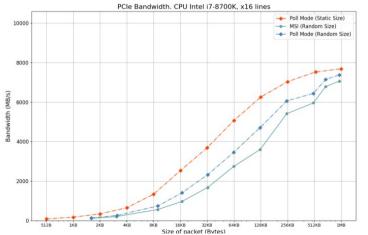

## Random-size packets PCIe

Random packets generator in the design

We use it to test and measure performance of PCIe interface

Runtime configuration – controlled by AXILite registers map via DAQ server

MVP for the next stages of DAQ

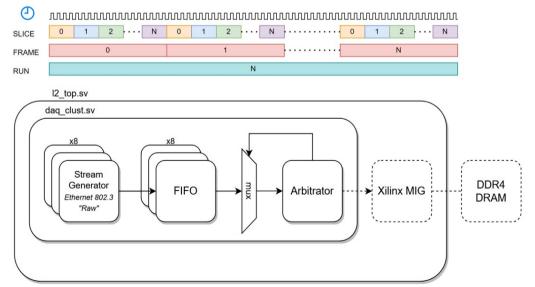

#### Data clusterization

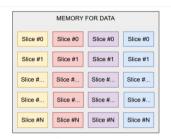

Рис. 8 – Буферизация в DDR4 DRAM

We use onboard PL DDR for data clusterization

Forward & store input parts of slices into a separate DDR memory locations

Then send them via PCIe to DAQ server

It signifactly improves performance of data transfers. It simplifies first stage data processing @ servers

#### Hardware activities

New mezzanine production & assembling confirmed by JINR

Kirill reflashed our oscilloscope. Now it's alive

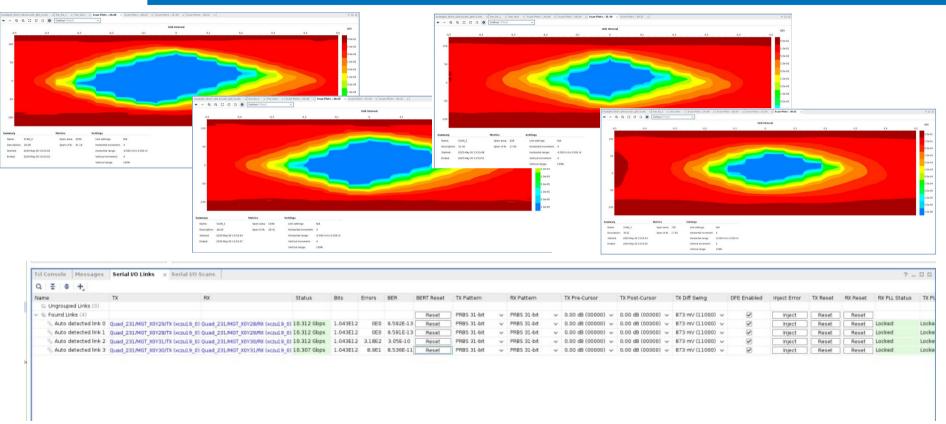

Issues: we observer high BER at 10G Ethernet links on our boards. We pushed all the buttons, but the reason is still unclear.

### 10G issues

## **Ongoings**

- Bringup of clusterization algorithm in simulator;

- Bringup onboard DDR for clusterization data;

- Dima is very close to his Bachelor degree;

- Investigation issues with 10G links: we did a lot, next steps are completely different evaluation board, then new fiber cables, then tests at JINR hardware

- Kirill and Dima on the way to visit to JINR. We prepare drafts of firmware, software and hardware which will be used and improved during visit